Innergy Quarx Action-Power Models

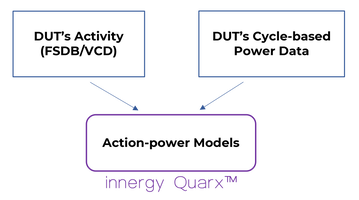

Action-Power Model BuildingInnergy Quarx builds statistical power models that identify actions within your design and the power consumed by those actions.

Actions are identified from a few key signals in the DUT's (Design Under Test) activity file (FSDB/VCD). Power is obtained from DUT's cycle-based power data. This data may be generated using Innergy Quarx, or obtained from your own power tool (Innergy Quarx works with all leading power tools). Examples of Actions: Actions can be small or large duration. Small duration actions: memory transaction, opcode execution, a table lookup etc. Large duration actions: packet routing configuration change, or an image processing algorithm change etc. |

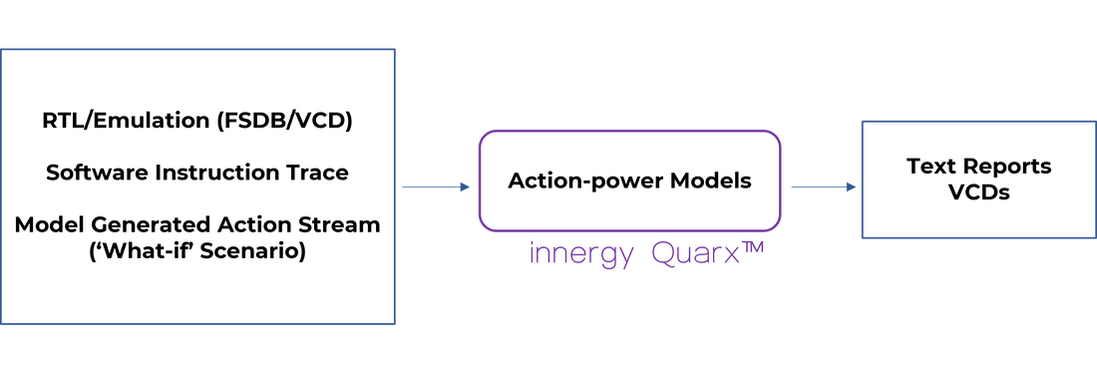

Action-Power Model UsageAction-power models may be used in simulation or for early 'what-if' power exploration. Models forecast power without needing any time- consuming gate simulations.

Early 'what-if' power exploration: Use model-generated power simulation to explore various 'what-if' power exploration scenarios:

|

User Experience

Model build process is efficient |

Easy integration with your existing tools |

|

We have made our build process very efficient by requiring few user inputs, and automation.

Typical model build duration is a few hours for a major design block. |

We work with all leading vendors in the EDA world to provide seamless integration into your tool flow.

|

Copyright© 2023 Innergy Systems Inc.